基于VHDL的分频器,程序源代码中完成对时钟信号CLK的2分频,4分频,8分频,16分频。

”VHDL 分頻器 2N分頻器5分頻器10分頻器分頻 计源码Quartus工程 FPGA“ 的搜索结果

VHDL Quartus 四分频器源代码-二进制位实现 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ---------------------------------------------- ENTITY...

2N分頻器5分頻器10分頻器分頻器器VHDL逻辑设计源码Quartus工程文件, Quartus软件版本9.0,可以做为你的学习设计参考。 ibrary ieee; use ieee.std_logic_1164.all; use ieee.std_logic_arith.all; use ieee.std_...

VHDL Quartus 四分频器源代码 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL; ---------------------------------------------- ENTITY clk_div IS ...

键控加/减计数器,将20MHz系统时钟经分频器后可得到5M、1M、100K、10K、5K、1K、10Hz、1Hz

VHDL Quartus 五分频器源代码 --半周期是原来半周期信号的N倍 --一个上升沿是2分频 --两个上升沿就是4分频 --三个上升沿就是6分频 LIBRARY IEEE; --调用库 USE IEEE.STD_LOGIC_1164.ALL;--调用包集合 USE IEEE.STD_...

quartusII 9.1可用于位同步提取电路的分频模块

基于VHDL语言分频器电路程序设计(汇总) 分频器简介: 分频器是数字电路中最常用的电路之一,在 FPGA 的设计中也是使用效率非常高的基本设计。基于 FPGA 实现的分频电路一般有两种方法:一是使用FPGA 芯片内部提供...

基于quartus ii平台用VHDL语言编程的4M分频器~~~~~~~~~~~~~~~~~~~

一个用VHDL语言编写的1/16分频器,后续还有计数器、数据选择器、七段数码显示程序等软件平台是Quartus II 7.2 ,最后通过这些小的模块可以组合起来制作出一个时钟或者其它的任意进制计数器,适合初学者,通过这些...

本文利用VHDL(甚高速集成电路硬件描述语言),通过Quartus Ⅱ 4.2开发平台,设计了一种能够实现等占空比的整数和近似等占空比的半整数分频器,这种设计方法原理简单,而且只需很少的CPLD逻辑宏单元。 1 设计原理 ...

vhdl代码实现分频器功能 频率该数字即可

使用VHDL编写的分频器。主频率为50MHZ,进行分频后得到1HZ的时钟。

可编程硬件描述语言VHDL Quartus 四分频器源代码.rar

50MHZ 分频至1MHZ,1KHz,1Hz 分频器

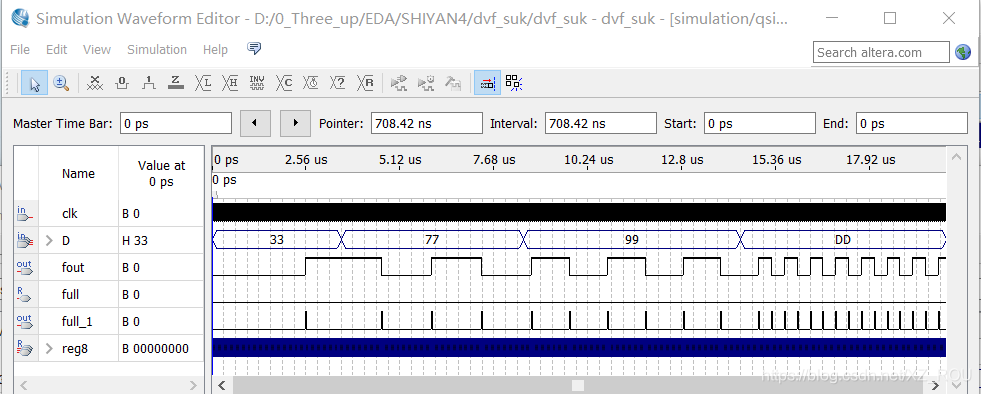

要求:在QuartusⅡ上进行编辑、编译、综合、适配、仿真,给出其所有信号的时序仿真波形。引脚锁定以及硬件下载测试...(时序仿真时CLK周期设5ns~10ns,D分别设33H,FEH)所编写的源程序如下:LIBRARYIEEE;USEIEEE.STD_...

VHDL频率分频器Quartus 9.0分频器项目。执照 Copyright 2006-2015 Canbin Lin ([email protected])Licensed under the Apache License, Version 2.0 (the "License");you may not use this file except in ...

可编程硬件描述语言VHDL Quartus 五分频器源代码.rar

可编程硬件描述语言VHDL Quartus 四分频器源代码-二进制位实现.rar

基于FPGA的小数分频器的设计与实现.doc基于FPGA的小数分频器的设计与实现【摘要】本文首先分析了现有小数分频器的优缺点,在此基础上提出了一种改进型小数分频器的设计方法。同时结合VHDL文本输入和原理图输入方式,...

数控分频器的设计摘要:此设计以quartusII为开发平台,用VHDL语言设计了数控分频器,并生成原理图,完成了分频的功能,并在quartusII上仿真,验证通过。关键词:QuartusIIVHDL语言数控分频器仿真...

VHDL实验分频器设计

标签: 分频器

分频器设计 实验目的 1. 熟悉QUARTUSII 软件的使用 2. 熟悉PLD设计流程 3. 学习分频器的设计 设计思路与框图 设计一个25位的二进制计数器,以50MHz时钟作为输入,然后将其最后一位引出即可得到大致为1Hz的输出。

vhdl设计FPGA读写DS18B20温度传感器quartus工程源码+文档说明 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity ds18B20 is port( clk :...

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity fenpin is port( clk:in std_logic; q:out std_logic ); end; architecture b1 of fenpin is ... sig...

用VHDL语言编写的数字分频器,已经过Quartus 5.0仿真调试。

基于双边沿检测技术获得时钟信号的倍频窄脉冲,利用该脉冲对时钟信号的...采用VHDL硬件描述语言和原理图输入方式,在QuartusⅡ平台下实现分频器的综合和仿真,并用ACEX1K30芯片实现.实验表明该方法的有效性和可靠性.

从网上下载了一段代码 但是关于分频器有点看不懂 library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity fenpin is port(clk:in std_logic; -- q:out std_logic_vector(9 downto 0...

推荐文章

- 阿里云企业邮箱的stmp服务器地址_阿里云stmp地址-程序员宅基地

- c++ 判断数学表达式有效性_高考数学大题如何"保分"?学霸教你六大绝招!...-程序员宅基地

- 处理office365登录出现服务器问题_o365登陆显示网络异常-程序员宅基地

- Nginx RTMP源码分析--ngx_rtmp_live_module源码分析之添加stream_ngx_rtmp_live_module 原理-程序员宅基地

- 基于Ansible+Python开发运维巡检工具_automation_inspector.tar.gz-程序员宅基地

- Linux Shell - if 语句和判断表达式_shell if elif-程序员宅基地

- python升序和降序排序_Python排序列表数组方法–通过示例解释升序和降序-程序员宅基地

- jenkins 构建前执行shell_Jenkins – 在构建之前执行脚本,然后让用户确认构建-程序员宅基地

- 如何完全卸载MySQL_mysql怎么卸载干净-程序员宅基地

- AndroidO Treble架构下HIDL服务查询过程_found dead hwbinder service-程序员宅基地